Bus I2C: asignación, dispositivo, transferencia de datos, direccionamiento

Al crear un circuito electrónico, muchos desarrolladores se enfrentan a la necesidad de utilizar una gran cantidad de chips intermedios para emparejar, muestrear y direccionar sus bloques individuales. Para minimizar la cantidad de chips auxiliares, Philips propuso una interfaz de red serial I2C bidireccional de dos hilos en la década de 1980, diseñada específicamente para administrar múltiples chips dentro de un solo dispositivo.

En la actualidad, solo Philips produce más de cien dispositivos compatibles con I2C para equipos electrónicos con una amplia variedad de propósitos: memoria, sistemas de procesamiento de video, convertidores de analógico a digital y de digital a analógico, controladores de pantalla, etc.

El bus I2C es una modificación del protocolo de intercambio de datos en serie capaz de transmitir datos en serie de 8 bits en el modo "rápido" habitual a velocidades de 100 a 400 kbps. El proceso de intercambio de datos se implementa aquí en solo dos cables (sin contar el cable común): línea SDA para datos y línea SCL para sincronización.

El bus se vuelve bidireccional debido a que las cascadas de salidas de los dispositivos conectados al bus tienen colectores o canales abiertos, replicando así el cableado AND. Como resultado, el bus minimiza la cantidad de conexiones entre chips, dejando menos pines y rastros necesarios en la placa. Como resultado, el propio tablero resulta ser más simple, más compacto y tecnológicamente más avanzado en producción.

Este protocolo le permite deshabilitar los decodificadores de direcciones y otra lógica de negociación externa. La cantidad de chips que pueden operar simultáneamente en el bus I2C está limitada por su capacidad: un máximo de 400 pF.

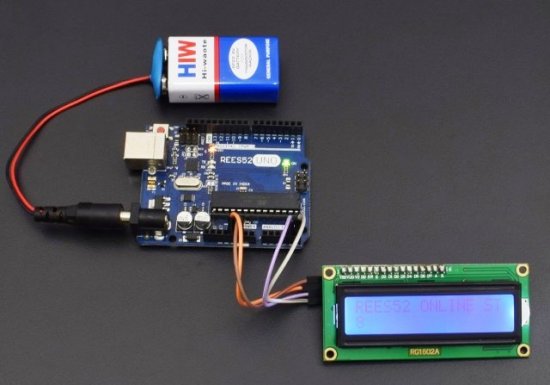

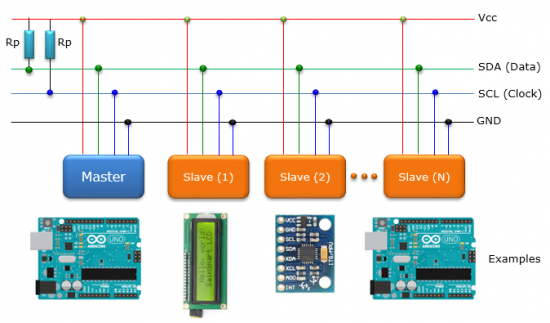

Los circuitos integrados compatibles con I2C tienen un algoritmo de supresión de ruido de hardware para garantizar la integridad de los datos incluso en presencia de fuertes interferencias. Dichos dispositivos tienen una interfaz que permite que los microcircuitos se comuniquen entre sí incluso cuando sus voltajes de alimentación sean diferentes. En la figura a continuación, puede familiarizarse con el principio de conectar varios microcircuitos a través de un bus común.

Cada uno de los dispositivos conectados al bus tiene su propia dirección única, está determinada por él y, de acuerdo con el propósito del dispositivo, puede funcionar como receptor o como transmisor. Al transmitir datos, estos dispositivos pueden ser maestros (master) o esclavos (slave). El maestro es el dispositivo que inicia la transferencia de datos y genera señales de reloj en la línea SCL. El esclavo, en relación con el maestro, es el dispositivo de destino.

En cualquier momento dado de operación en el bus I2C, solo un dispositivo puede actuar como maestro; genera una señal en la línea SCL.Un maestro puede ser un receptor maestro o un transmisor maestro.

En principio, el bus permite varios maestros diferentes, pero impone restricciones en las características de formar señales de control y monitorear el estado del bus; esto significa que varios maestros pueden comenzar a transmitir al mismo tiempo, pero los conflictos de este tipo se eliminan gracias al arbitraje, es decir, la forma en que se comporta el maestro cuando detecta que el bus está ocupado por otro maestro.

La sincronización de un par de dispositivos está asegurada por el hecho de que todos los dispositivos están conectados al bus, formando un cableado "Y". Inicialmente, las señales SDA y SCL son altas.

COMENZAR y PARAR

El intercambio comienza con el maestro generando el estado «START»: en la línea SDA, la señal pasa de estado alto a bajo, mientras que la línea SCL tiene un nivel alto estable. Todos los dispositivos conectados al bus perciben esta situación como un comando para iniciar el intercambio.

Cada maestro genera una señal de reloj individual en la línea SCL cuando transmite datos en el bus.

El intercambio finaliza con la formación del estado STOP por parte del maestro: en la línea SDA la señal cambia de bajo a alto, mientras que la línea SCL tiene un nivel alto estable.

El conductor siempre actúa como fuente de las señales de ARRANQUE y PARADA. En cuanto se fija la señal de «INICIO», significa que la línea está ocupada. La línea está libre cuando se detecta una señal de STOP.

Inmediatamente después de declarar el estado START, el maestro cambia la línea SCL a nivel bajo y envía el bit más significativo del primer byte del mensaje a la línea SDA. El número de bytes en un mensaje no está limitado.Los cambios en la línea SDA se habilitan solo cuando el nivel de la señal en la línea SCL es bajo. Los datos son válidos y no deben cambiarse solo cuando el pulso de sincronización es alto.

El reconocimiento de que el receptor esclavo ha recibido el byte del transmisor maestro se realiza configurando un bit de reconocimiento especial en la línea SDA después de que se haya recibido el octavo bit de datos.

LA CONFIRMACIÓN

Por lo tanto, enviar 8 bits de datos desde el transmisor al receptor termina con un pulso adicional en la línea SCL cuando el dispositivo receptor se queda bajo en la línea SDA, lo que indica que ha recibido el byte completo.

La confirmación es una parte integral del proceso de transferencia de datos. El maestro genera un pulso de sincronización. El transmisor envía un estado bajo a SDA mientras el reloj de reconocimiento está activo. Mientras el pulso de sincronización es alto, el receptor debe mantener el SDA bajo.

Si el esclavo de destino no reconoce su dirección, por ejemplo porque actualmente está ocupado, la línea de datos debe mantenerse alta. El maestro puede entonces dar una señal de STOP para abortar el envío.

Si la recepción la lleva a cabo el receptor maestro, entonces está obligado a informar al transmisor esclavo después de completar la transmisión, no confirmando el último byte. El transmisor esclavo libera la línea de datos para que el maestro pueda emitir una señal de PARADA o una señal de INICIO repetida.

La sincronización de los dispositivos está asegurada por el hecho de que las conexiones a la línea SCL se realizan según el principio "Y".

El maestro no tiene el derecho exclusivo de controlar la transición de la línea SCL de menor a mayor.Si el esclavo necesita más tiempo para procesar un bit recibido, puede mantener SCL bajo de forma independiente hasta que esté listo para recibir el siguiente bit de datos. La línea SCL en tal situación estará baja durante la duración del pulso de sincronización de bajo nivel más largo.

Los dispositivos con la baja sostenida más baja permanecerán inactivos hasta que finalice el período largo. Cuando todos los dispositivos hayan terminado el período de sincronización baja, SCL subirá.

Todos los dispositivos comenzarán a marcar alto y el primer dispositivo en completar su período será el primero en establecer la línea SCL baja. Como resultado, la duración del estado bajo de SCL estará determinada por el estado bajo más largo del pulso de sincronización de uno de los dispositivos, y la duración del estado alto estará determinada por el período más corto de sincronización de uno de los dispositivos. dispositivos.

Los receptores pueden utilizar las señales de sincronización como un medio para controlar la transmisión de datos a nivel de bit y byte.

Si el dispositivo es capaz de recibir bytes a una velocidad alta, pero tarda cierto tiempo en almacenar el byte recibido o prepararse para recibir el siguiente byte, puede continuar manteniendo SCL bajo después de recibir y reconocer un byte, forzando el transmisor en un estado de espera.

Un microcontrolador sin circuitos de hardware integrados, por ejemplo a nivel de bits, puede ralentizar la velocidad del reloj aumentando la duración de su estado bajo. Como resultado, la velocidad en baudios del dispositivo maestro estará determinada por la velocidad del dispositivo más lento.

DIRECCIONAMIENTO

Cada dispositivo conectado al bus I2C tiene una dirección de programa única en la que el maestro lo direcciona mediante el envío de un comando específico. Los microcircuitos del mismo tipo se caracterizan por un selector de direcciones, implementado en forma de entradas digitales del selector o en forma analógica. Las direcciones se dividen en el espacio de direcciones de los dispositivos conectados al bus.

El modo normal asume el direccionamiento de siete bits. El direccionamiento funciona de la siguiente manera: después del comando «START», el maestro envía el primer byte, que determina qué dispositivo esclavo se necesita para comunicarse con el maestro. También hay una dirección de llamada común que define todos los dispositivos en el bus, todos los dispositivos (teóricamente) responden con un reconocimiento, pero en la práctica esto es raro.

Entonces, los primeros siete bits del primer byte son la dirección del esclavo. El bit menos significativo, el octavo, indica la dirección de envío de datos. Si hay un «0», entonces la información se escribirá desde el maestro a este esclavo. Si es «1», la información será leída por el maestro de este esclavo.

Una vez que el maestro termina de enviar el byte de dirección, cada esclavo compara su dirección con él. Cualquier persona con la misma dirección es un esclavo y se define como transmisor esclavo o receptor esclavo, según el valor del bit menos significativo del byte de dirección.

Una dirección esclava puede incluir partes fijas y programables. Muy a menudo, una gran cantidad de dispositivos del mismo tipo funcionan en un sistema, luego la parte programable de la dirección permite el uso de un máximo del mismo tipo de dispositivos en el bus. La cantidad de bits programables en el byte de dirección depende de la cantidad de pines libres en el chip.

A veces, un pin con una configuración analógica del rango de direcciones programable es suficiente, por ejemplo, el SAA1064, un controlador de indicador LED que tiene exactamente esa implementación. El potencial de un pin en particular determina el desplazamiento del espacio de direcciones del chip para que los chips del mismo tipo no entren en conflicto al operar en el mismo bus. Todos los chips que admiten el bus I2C contienen un conjunto de direcciones que el fabricante especifica en la documentación.

La combinación «11110XX» está reservada para direccionamiento de 10 bits. Si imaginamos el intercambio de datos del comando «START» al comando «STOP», se verá así:

Aquí se permiten formatos de intercambio de datos simples y combinados. El formato combinado significa que entre «START» y «STOP» el maestro y el esclavo pueden actuar como receptores y transmisores, esto es útil, por ejemplo, en la gestión de memoria serie.

Deje que el primer byte de datos transfiera una dirección de memoria. Luego, repitiendo el comando «START» y leyendo la dirección del esclavo, los datos de la memoria funcionarán. Las decisiones de aumentar o disminuir automáticamente la dirección a la que se accedió anteriormente las toma el desarrollador del dispositivo después de haber estudiado previamente la documentación del chip. De una forma u otra, después de recibir el comando START, todos los dispositivos deben restaurar su lógica y prepararse para el hecho de que ahora se nombrará la dirección.